这些关于芯片CP测试的“黑话”,你都能get吗?

时常能听到这样的对话:

Mike:Amy,新产品已经TO了,预计5月Wafer会出来。

Amy:太好了,我们第一批先做blind assembly,CP下一批做。

Mike:OK,Probe card和handler也定下去了,4月就能到。

一入“芯”学深似海,术语多到一脸懵。作为一流的国产汽车电子芯片供应商,智芯半导体在过去近两年的出货中,因出色的保供能力和优秀的质量表现而倍受客户的好评,这与公司生产运营部门对生产测试的严格把控息息相关。这就不得不谈一谈关于芯片测试的那些事了,以上对话就围绕着芯片CP测试展开。听不懂别着急,今天就来和大家聊一聊芯片测试中的CP测试,唠一唠CP测试中的那些“黑话”。

为什么要做芯片测试?

任何芯片,无论设计得多么完美,也很难避免在生产过程中的种种问题而导致的芯片缺陷。芯片生产过程中的问题包括:金属线开路或者短路、注入掺杂不够、制程或掩膜错误、金属metal层桥接问题、过孔的开路问题、CMOS晶体管常开/常关、制程问题导致晶体管trans过慢、材料缺陷——大块缺陷(裂纹、晶体缺陷),表面杂质(离子迁移)、介质击穿、电迁移(线很细,电流很大,电子冲击连接处,慢慢接触部分越来越细)、接触点退化、封装密封泄露等等。因此必须对芯片进行严格的测试,才能避免“设计美如画、生产很拉跨”的现象,保证交付给客户的产品是零缺陷。

芯片需要哪些测试?

芯片测试分为CP和FT两个阶段。

CP不是“CouPle”,CP是指Circuit probe,就是在未进行封装的整片晶圆上,利用很多细细的探针扎到裸露的芯片上,再将探针的另外一端连接至测试机来进行的测试,听起来像是对芯片进行带电针灸。

FT测试(Final Test)是把芯片放在Socket(卡座)中,芯片的引脚和卡座中的金属丝接触,这些金属丝通过Socket板上的连接线连接至测试机台,测试机台根据测试工程师编写好的测试程序对芯片进行测试。这个测试和人做心电图测试有点类似。

CP测试的目的

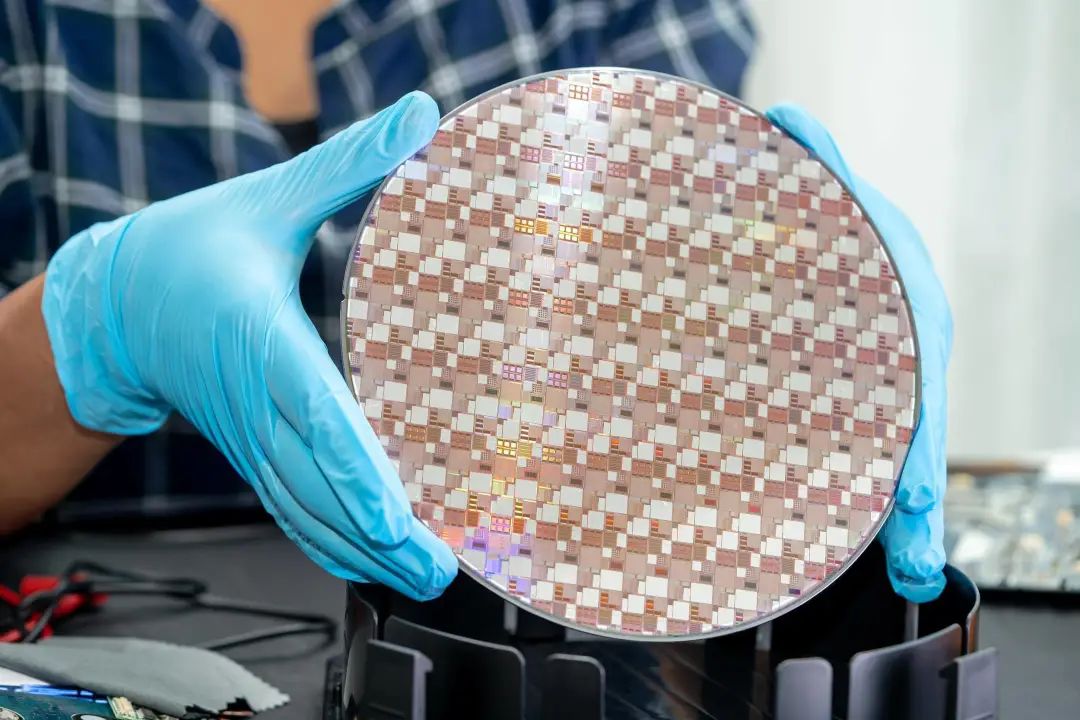

CP测试常应用于芯片的功能测试与性能测试。制作完成的晶圆(Wafer)上规则分布着未封装的芯片(裸DIE,晶粒),这其中会有一定量的因生产工艺等原因导致的残次品。CP测试的目的就是对这些裸DIE做电性功能方面的测试,以便在进入封装阶段之前将电性功能不良的芯片筛除(Wafer Sort),从而节省封装成本,提高产品的良率(Yield)。

图1排列着裸DIE的晶圆,图片源自网络

在这一阶段,芯片的管脚均裸露在外,这些细小的管脚就需要通过更细的探针(Probe)来与测试机台(Tester)相连接。CP测试的主要设备就是探针平台,包括夹持不同规格芯片的夹具;辅助设备则是无尘室及其全套设备。如前所述,芯片封装后,有些管脚被封装在内部,而FT测试无法使用探针测试芯片内部,因此芯片的有些功能只能在CP测试中进行。

CP测试的内容

1.SCAN:检测芯片逻辑功能是否正确。

2.Boundary SCAN:检测芯片管脚功能是否正确。

3.存储器:芯片通常集成着各种类型的存储器(如ROM/RAM/Flash),因此常在设计时提前加入BIST(Built-In Self Test)逻辑,用于自测存储器读写和存储功能。CP测试时,芯片通过特殊的管脚配置进入各类BIST功能,完成自测后BIST模块将测试结果反馈给测试机台。

4.DC/AC Test:DC测试包括芯片Signal PIN的Open/Short测试,电源PIN的Power Short测试,以及检测芯片直流电流和电压参数是否符合设计规格;AC测试检测芯片交流信号质量和时序参数是否符合设计规格。

5.RF Test:检测RF模块逻辑功能是否正确。

6.其他Function Test:检测芯片其他重要的功能和性能是否符合设计规格。

CP测试的准备工作

1.可测试性设计(DFT-Design For Test)

如果把CP测试比作对裸Die的一场“体检”,那么CP测试的内容就是这些Die的体检项目,而DFT则是针对这些项目所作出的一系列预先安排,确保体检可以顺利进行。可测试性设计是一种将特殊结构在设计阶段植入电路的方法,以便生产完成后进行测试,确保检测过后的电子组件没有功能或制造上的缺陷。它通常包含SCAN、Boundary SCAN、各类BIST、各类Function Test Mode(功能测试模式)以及一些Debug Mode(调试模式)。测试人员需要在芯片设计之初就准备好Test Plan(测试计划),根据芯片的规格参数规划好测试内容和测试方法。通常会准备若干种功能测试模式,通过配置管脚使芯片进入指定的测试状态,从而完成各个类型的测试。

2.选择测试厂&测试机

DFT完成后,就可以开始准备“体检器材和设备”了:根据芯片类型、测试内容、测试规格和成本等因素,选择测试厂和测试机。一套芯片自动测试设备称为ATE(Automatic Test Equipment),由Tester(机台)、Load board(测试板)、Probe Card(探针卡)、Handler(机械臂)和测试软件等部分组成。

3.制作探针卡以及测试程序

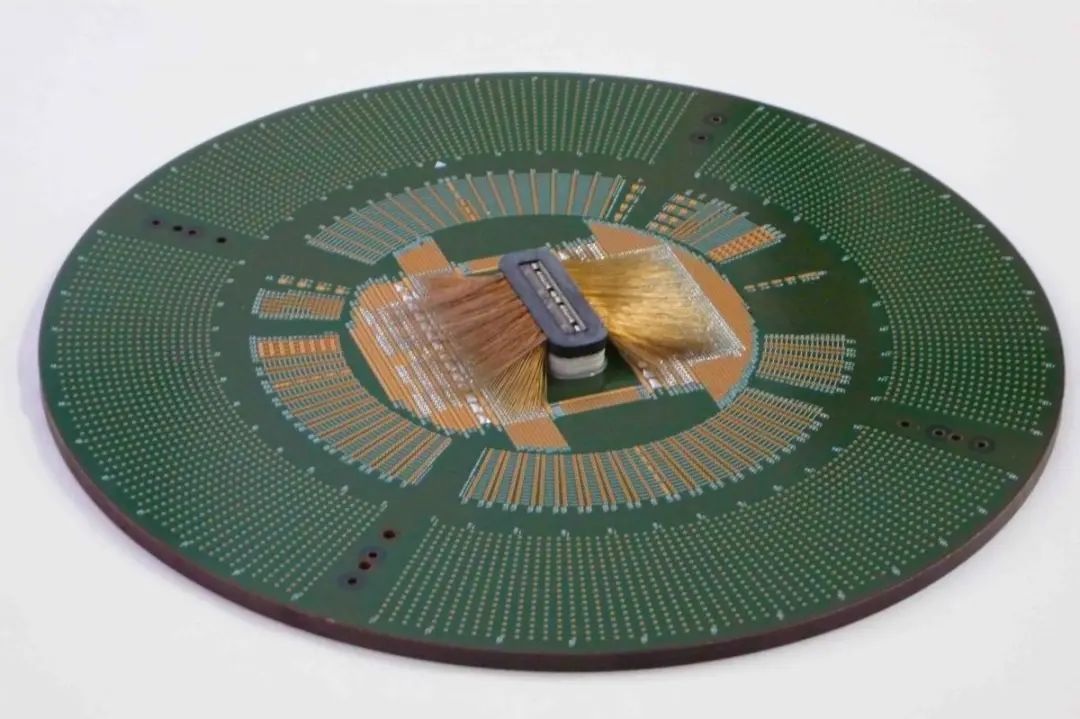

选择好测试机后,需要根据芯片的规格制作探针卡,并开发针对被测芯片的测试程序(Test Program)。

探针卡包括探针和芯片外围电路。探针的位置和晶圆上的裸DIE的位置和规格。另外为了提高测试效率,降低测试成本,可以制作同时测多个DIE的针卡。Site就是指可以同时测量DIE的数目,一般同侧数是有上限的。

图2探针卡,图片源自网络

4.调试以及结果分析

CP测试程序需要用几片晶圆经过调试后,生成最终的量产测试程序。

根据Test Plan,Pattern(测试向量)被分作不同的BIN(分类),从而定位测试错误的位置。在CP测试这场“体检”中,测试机台就是一个大“医院”,而不同的BIN则是医院的一个个科室;每颗裸Die都要到一个个BIN中去进行“体检”,也就是测试,测试后不符合要求的就会被筛出。当然也不是每一颗Die都会测完所有的BIN,这个后面会说到。调试时还可以在系统上直接看到一个Pattern中错误的Cycle位置,工程师根据这些错误信息进行debug(调试),修改Pattern和测试程序,逐个清理所有的bug,直到所有BIN都PASS。

同测的多Site全部PASS,循环多轮后,便可以在整片晶圆上Try Run。此时工程师还要调试探针力度、清理探针周期等参数,探针扎到晶圆的力度太大会造成晶圆损伤和探针的磨损,力度太轻会造成接触不良。探针经过多次测试以后,会有磨损,会定期更换。确保整片晶圆上每一次Touchdown(下针)都可以测试稳定。

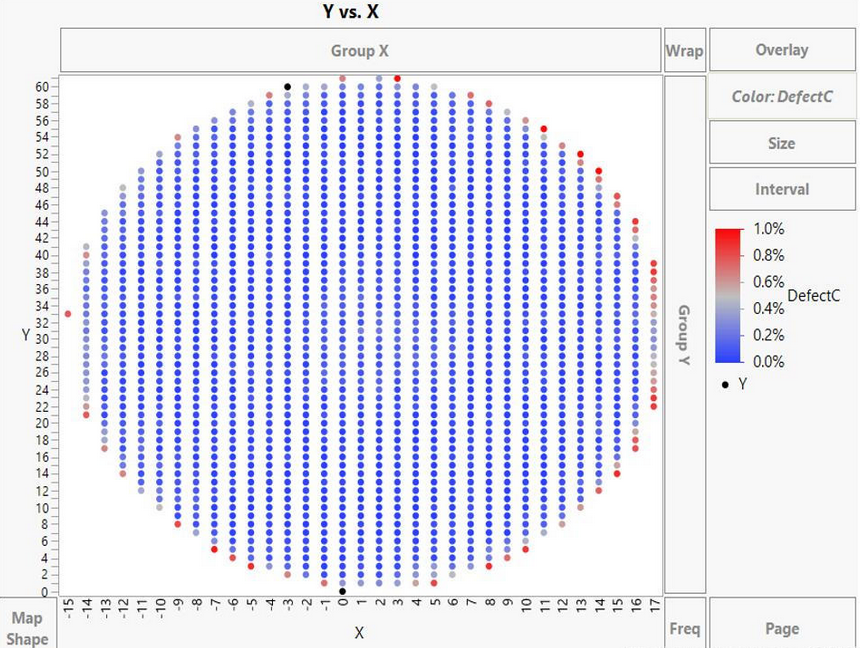

整片晶圆的测试结果通常生成一个Wafer Map(晶片图)文件,数据生成一个记录文件(datalog,例如STD文件),这就是裸Die的“体检报告”。Wafer Map主要包含良率、测试时间、各BIN的错误数和DIE位置,datalog则是具体的测试结果。工程师通过分析这些数据,决定是否进入量产。

图3 Wafer Map截图,图片源自网络

量产时的CP测试

进入量产阶段后,采用专业软件,对大量CP测试的统计数据进行分析,可以对测试流程进行优化,进一步提高测试效率。

例如,根据结果将错误率较高的BIN排在前面测试,当测试进行到第一个出错的BIN后就不再继续向下进行,从而节省测试时间,并减少后续测量造成针卡的磨损;这就像飞行员筛选体检时,如果把视力检查作为体检的第一项,那么有些视力不够好的同学在测完这第一项后就可以被直接淘汰,后面的检查也没有必要再进行了。又比如,将错误率较低的BIN排在靠后的位置,甚至删除错误率极低的BIN的测试,以提高测试效率;对于出错率较高的处于晶圆边缘位置的DIE,有时可以直接剔除,不进行测试就标为坏品。

根据统计数据,如果有些错误概率很低的DIE,还可以进行复测。对于首次测试出错的DIE,再重新测试一次可能会PASS,因此复测可以避免偶发因素带来的错误,提高良率,但复测会加长测试时间,因此要综合考虑决定是否复测。

量产时,还需要关注良率数据的稳定性,当连续出现良率较低的情况时,需要停止测试,进行数据分析,并对测试设备进行检查,排除测试设备的问题后如果良率还是很低,就需要与晶圆厂沟通,晶圆厂需要检查晶圆生产过程是否出现异常。

经过CP测试的晶圆将会被送至封装厂,封装厂根据Wafer map的数据对晶圆进行切割后,将好的DIE挑选出来进行封装。封装好的芯片将送至测试厂进行FT(Final Test)。后面我们将继续介绍FT的“黑话”。